taigon 교수님 논리회로설계에서 사용하는 tool인 xilinx사의 vivado 사용법입니다!

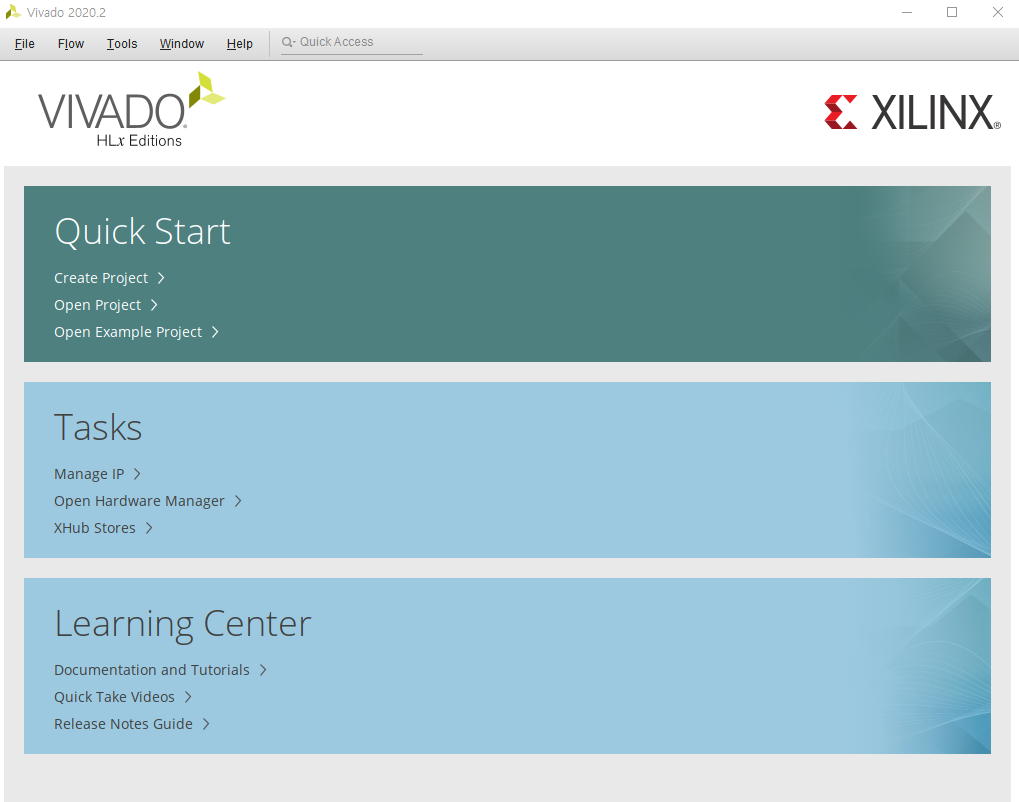

우선 vivado 2020.2를 실행합니다. xilinx 홈페이지 https://www.xilinx.com/support/download.html 에서 tool을 다운로드 받을 수 있습니다. 용량이 상당히 크니(약 60G) PC 용량 확인 후 설치하시기 바랍니다.

여기서 2020.2 버전을 사용하는 이유는 무료버전인 Webpack이 2020.2 까지 제공되기 때문입니다. 최신버전은 유료 라이센스를 구입하여 사용해야 합니다. 저는 아무것도 모르고 최신버전을 다운받아서 라이센스 해결하느라 4시간 날려먹고 2020.2 Webpack을 재설치했습니다. 저처럼 시간버리시는 분들이 없기를..

vivado를 설치한 후 실행 합시다.

위와 같은 창이 나타나네요. Quick Start → Create Project 를 클립해줍니다.

그럼 이런 창이 나타나는데 Next 클릭하고 다음 나타나는 창에서 프로젝트 이름과 경로를 지정해줍니다.

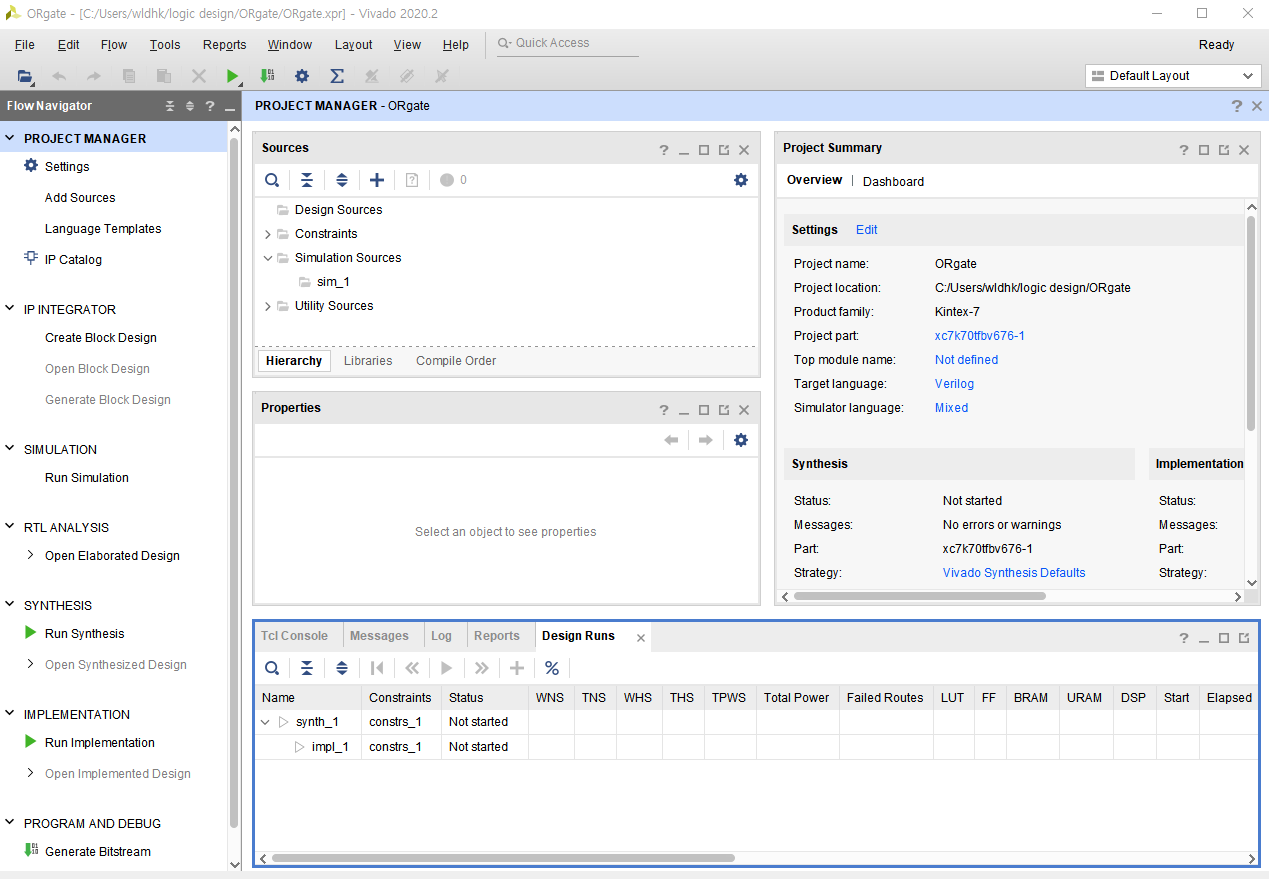

저는 ORgate를 만들어볼거라서 프로젝트 이름을 ORgate로 해주었습니다.

그리고 중간에 세부설정할 수 있는 창이 뜨는데 Next를 계속 눌러서 넘어갑니다. 마지막으로 Finish를 클릭해서 프로젝트를 생성합니다.

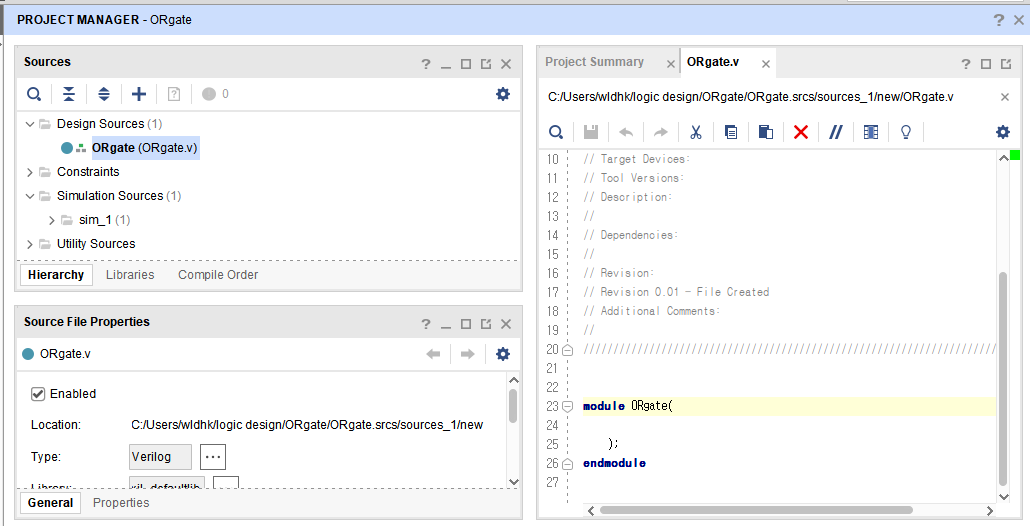

프로젝트를 생성한 후 초기화면입니다. verilog 파일을 생성해주기 위해 화면 중간에 있는 Sources의 Design Source 폴더에서 .v 확장자를 가진 파일을 생성해줍니다.

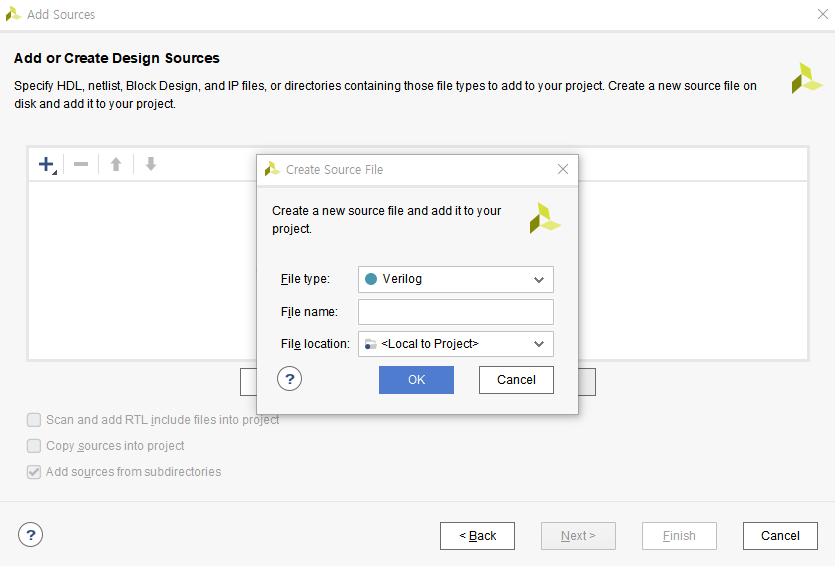

Add Source → Create File 을 클릭하시고 verilog 파일을 생성해줍니다.

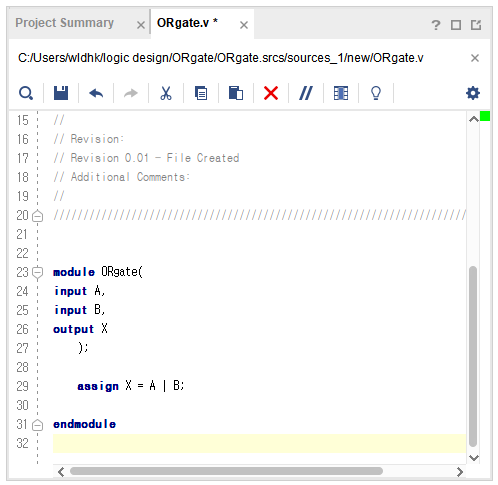

verilog 파일을 생성한 화면입니다. 오른쪽의 편집창에서 코드를 작성할 수 있습니다.

testbench는 Simulation Sources에서 위와 같은 과정으로 생성할 수 있습니다. 이때 파일명은 ORgate_tb.v로 설정해줍니다.

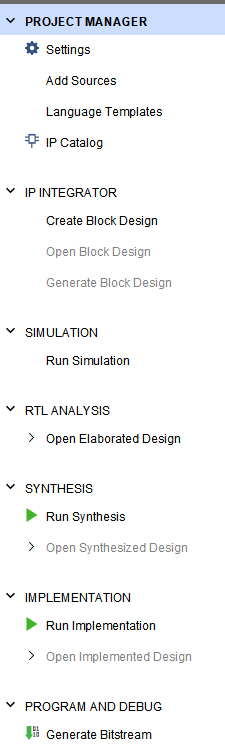

코드 작성을 마치고 왼쪽 상태창의 Run Synthesis을 클릭해 논리합성을 해줍니다. 그 후 Run Simulation을 왼쪽 클릭하여 Behavioral Simulation을 클릭하면 작성한 코드를 시뮬레이션 할 수 있습니다.

ORgate를 data flow level로 작성했습니다. 그리고 testbench를 만들어 줍시다. testbench에 대한 설명은 따로 게시물로 만들어볼 생각입니다.

'EE > Digital Design' 카테고리의 다른 글

| [Synopsys EDA] Post-Synthesis simulation (0) | 2022.11.02 |

|---|---|

| [Degital Design] 2D Systolic Array for matrix multiplication (0) | 2022.09.30 |