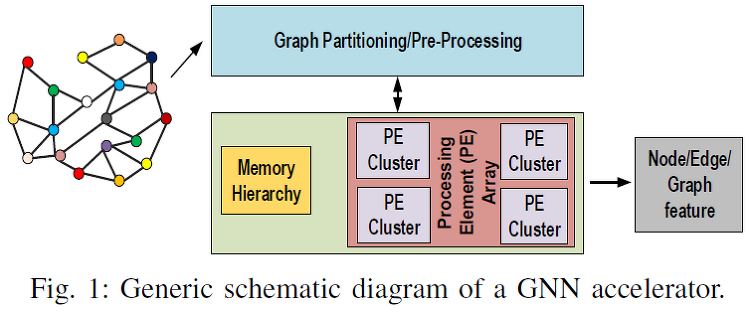

현재 팀장으로서 GCN 가속기 설계 프로젝트를 진행하고 있습니다. 11월 21일까지 ACM/IEEE DAC(Design Automation Conference)에 투고할 논문을 작성하는 것이 목표입니다. 어쩌다 보니 시간이 한 달 남았는데, 잘할 수 있겠죠..? 교수님 말로는 DAC 정도 수준의 학회에 논문을 낸다면 인더스트리에서든 아카데미아에서든 절대 무시당하지 않을 거라고 합니다. 아직 감은 오지 않지만 이 정도로 동기부여를 받고 열심히 해보려고 합니다. 제가 쳐내야 할 일들과 저희 조가 쳐내야 할 일들을 정리해보면 다음과 같습니다. 1. 내가 쳐내야 할 일 1.1 Ramulator Setting 1.2 HyGCN의 Combination engine RTL design, synthesis, STA 1..