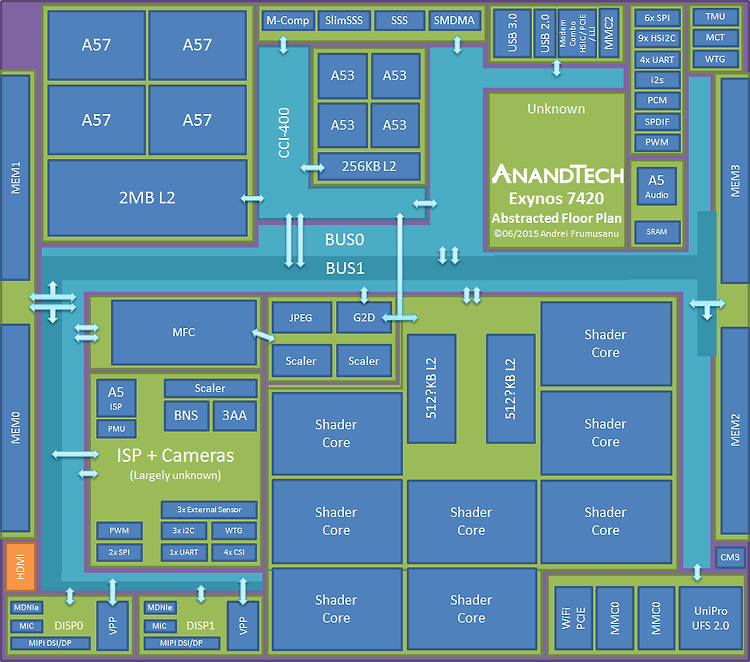

SoC분야에서 IP(Intellectual Property)는 재사용이 가능하도록 잘 정리, 정의된 모듈을 의미합니다. 이때 IP를 재사용하는 이유는 처음부터 재설계를 하면 개발시간이 너무 오래걸리기 때문입니다. 이는 time to market을 떨어트리고 결국 chip을 생산하는 회사의 수익감소로 이어져서, 대부분의 SoC 제조사들은 ARM 사에서 IP를 구입해서 개발을 진행한다고 합니다. 위 사진은 삼성에서 만든 AP(Application processor)인 Exynos 7420입니다. 이러한 Architecture만을 통해서는 동작을 자세히 이해할 수는 없지만, core, cache, ISP 등이 bus(ABMA라는 protocol을 따릅니다.)를 통해 interconnected된 것을 확인할 수..